Due to recent changes by Oracle, java applets have become difficult to run in the browser. To mitigate the troubles, Oracle has provided the following websites to help users troubleshoot: and Even after following the above instructions, loading applets may still show warning concerning “unsigned application” and “unknown publisher”. For Teahlab in particular, these warnings are due to the fact that we have opted not to pay a third party such as Verisign to sign our applets. Any warning that comes up when you try to run our applets should emphasize that our applets will always run with “limited access”, which is Oracle’s way of letting you know that teahlab doesn’t do anything on your computer except running the circuits you see: in other words, our applets are safe to run. Sincerely, The Teahlab Team.

I have been working on a vhdl program that accepts 2 inputs, a 3-bit input and a 4-bit input. The 3-bit input represents '2 to the power of n', ie an input of 010(which is 2) would equal 2^2=4. An input of 110(which is 6) would yield 2^6 which is 64.

This is to be multiplied by a 4-bit input from 0000 to 1111, and the answer stored as 8-bits. However, when I try to solve for this in VHDL, I keep getting the error 'Expression error at midtermqone.vhd(34): expression has 12 elements, but must have 8 elements'. I am new to VHDL, and searching online has yielded little result. I want a way for my output, in this case hex, to store the product of my 2 inputs as an 8 bit value but don't know how. Any help would be greatly appreciated and below is my code.

Library IEEE; use IEEE.STDLOGIC1164.ALL; use IEEE.STDLOGICARITH.ALL; use IEEE.STDLOGICUNSIGNED.ALL; entity midtermqone is port(en: in stdlogic; reset: in stdlogic; threebit: in stdlogicvector(2 downto 0); fourbit: in stdlogicvector(3 downto 0); hex: out stdlogicvector(7 downto 0) ); end midtermqone; architecture arch of midtermqone is signal temp: stdlogicvector(7 downto 0); begin process(en, reset, threebit, fourbit) begin if(reset = '1') then temp temp temp temp temp temp temp temp temp. Multiplication of the 8-bit temp with the 8-bit fourbit gives a 12-bit result, which is assigned to the 8-bit hex, thus the error message 'expression has 12 elements, but must have 8 elements'. Suggestion: Get ridge of the non-standard (Synopsys) STDLOGICARITH and STDLOGICUNSIGNED, and start using the standard numericstd package. With the numericstd you can resize the result using: library ieee; use ieee.numericstd.all. I could see two ways to get rid of the error. The simplest is: architecture simple of midtermqone is begin process (en, reset, fourbit, threebit) begin if reset = '1' then hex '0'); elsif en = '1' then hex '0'); elsif en = '1' then intermed:= SHL('0000' & fourbit, threebit); end if; hex '0'); elsif en = '1' then intermed:= SHL('0000' & fourbit, threebit); end if; if intermed(11) = '1' or intermed(10) = '1' or intermed(9) = '1' or intermed(8) = '1' then hex.

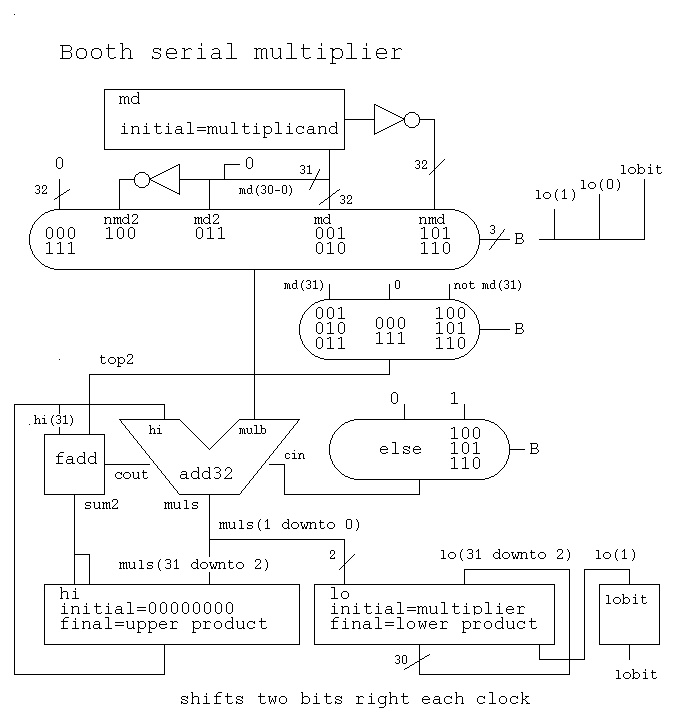

The goal is to design and simulate an 8-by-8 bit shift/add multiplier. The result is a completely synthesized 8-by-8 bit and 32-by-32 bit shift/add multiplier with various design options for speed and area. The associated VHDL source code is included in Appendix A: VHDL Source Code. VHDL Modeling for Synthesis Hierarchical Design Textbook Section 4.8: Add and Shift Multiplier “Add and shift” binary multiplication Shift & add Shift & add. System Example: 8x8 multiplier. SerIn: in std_logic --Serial input); end RegN; Generic N-bit register architecture.